## **Microelectronics Circuits**

Sixth Semester B.E. Degree Examination, Jan./Feb. 2021

Time: 3 hrs.

Max. Marks:100

Note: Answer any FIVE full questions, selecting THREE questions from Part-A and TWO questions from Part-B.

- Explain the implementation of biasing circuit by fixing V<sub>G</sub> and connecting a resistance in the 1 source with neat diagram. (06 Marks)

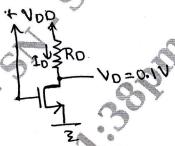

- Design the circuit in Fig.Q1(b) to establish a drain voltage of 0.1V. What is the effective resistance between drain and source at this operating point. Let V<sub>t</sub> = 1V,

$$K_n'\left(\frac{W}{L}\right) = 1 \text{ mA/V}^2$$

Fig.Q1(b)

(06 Marks)

- Explain common gate amplifier with neat circuit diagram and small signal equivalent circuit. (08 Marks)

- Compare MOSFET and BJT in terms of: 2

- Low frequency hybrid  $\pi$  model

- Current voltage characteristics (ii)

(06 Marks)

- (iii) High frequency model With relevant equations and neat circuit diagram, explain working of MOS steering circuits.

- (08 Marks)

- With neat diagram, explain working of basic MOS current mirror circuit.

(06 Marks)

- Draw high frequency equivalent circuit model of common source amplifier and analyze 3 a. using Miller's theorem. (08 Marks)

- Analyze common base amplifier to find R<sub>in</sub> and R<sub>out</sub>. b.

(07 Marks)

- How does cascade MOS current mirror improves the performance of current mirror circuit? (05 Marks)

- With neat diagrams, explain small signal operation of MOS differential pair. Derive expression for differential gain.

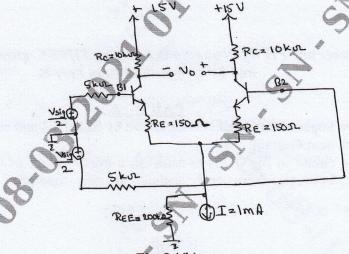

- For circuit in Fig.Q4(b), the differential amplifier uses transistor with  $\beta = 100$ . Evaluate:

- Input differential Resistance Rid

- Overall differential gain  $\frac{V_0}{V}$  (neglect effect of  $r_0$ )

## 10EC63/10EC638

- (iii) The worst case common mode gain if the 2 collector resistances are accurate to within ±1%.

- (iv) The CMRR in dB.

- (v) The input common mode resistance (assume  $V_A = 100 \text{ V}$ )

Fig.Q4(b) (10 Marks)

- 5 Write short notes on:

- a. T-equivalent circuit model of MOSFET

- b. Multistage amplifiers

- c. Source follower

- d. Current source

(20 Marks)

## PART – B

- 6 a. Explain the three properties of negative feedback. (09 Marks)

- b. Draw and explain Nyquist plot of an unstable amplifier. (05 Marks)

- c. With graph, explain how stability analysis is done using bode plot. (06 Marks)

- 7 a. With neat diagram, explain a single op amp difference amplifier and derive an expression for differential gain Ad. (07 Marks)

- b. Briefly explain logarithmic amplifier and derive an expression for output voltage. (08 Marks)

- e. Explain basic principle of sample and hold circuit using basic circuit. (05 Marks)

- 8 a. Write a short note on domino CMOS logic circuits. (06 Marks)

- b. Implement  $F = AB + \overline{A} \overline{B}$  using AOI gate logic. (08 Marks)

- c. Explain the Voltage Transfer Characteristics (VTC) of CMOS inverter when Q<sub>N</sub> and Q<sub>P</sub> are matched. (06 Marks)

\* \* \* \* \*

- --